Product Details

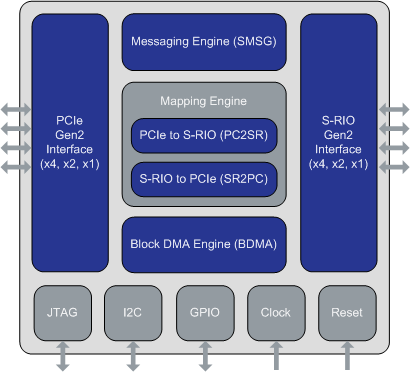

- x4 PCIe V2.1 to x4 S-RIO V2.1

- Single port: x4, x2 or x1 support

- 1.25, 2.5, 3.125 and 5 Gbaud support

- Multiple DMA and Messaging channels/engines each capable of supporting full 20 Gbaud I/O

- 8Kbyte packet buffering per DMA and Messaging Channel

- 20 Baud line rate performance for 64 byte or larger packets, max TLP payload 256 bytes, max block DMA 64 Mbyte

- PCI Express non-transparent bridging for transaction mapping

- Lane reversal

- Automatic Polarity inversion for PCI Express

- Typical power 2W

- Reach Support: 60 cm over 2 connectors

- 100, 125, 156.25 MHz S-RIO and PCIe Endpoint compatible clocking options

- JTAG 1149.1 and 1149.6

- 13x13 mm FCBGA

- Industrial and Commercial options

The Tsi721 converts from PCIe to RapidIO and vice versa and provides full line rate bridging at 20 Gbaud. Using the Tsi721 designers can develop heterogeneous systems that leverage the peer to peer networking performance of RapidIO while at the same time using multiprocessor clusters that may only be PCIe enabled. Using the Tsi721, applications that require large amounts of data transferred efficiently without processor involvement can be executed using the full line rate block DMA+Messaging engines of the Tsi721.

Learn more: IDT RapidIO Development Systems